コマンド解説-応用編その3:パスワードドアを作ってみよう!上級編-

投稿日:2021/02/20

最終更新日:2021/02/20

どうも、ユキミ大福です。

今回はMinecraft統合版のコマンドの応用法として、パスワードドアを作ってみます。今回はその上級編です。

ここで解説するコマンド等は、解説する注意事項等をよく読み、個人でより詳しく調べた上で、個人の責任において使用して下さい。コマンド等の使用によって如何なる損害が発生しても、筆者であり当ブログの管理者でもあるわたくしユキミ大福は一切の責任を負いかねますので、ご了承下さい。

前回のおさらい

前回は少し高度なパスワードドアを作りました。パスワードドアとは、一定のパスコードを入力することで開くドアのことでした。この辺の基礎については初級編 ↓ をご覧下さい。

そして前回はその過程でLatch(FlipFlop)回路について解説しました。Latch回路とは1ビットの情報を保存できる回路でしたね。

今回の内容も前回の内容が基礎となっているため、まだイマイチ理解できていない方は前回の記事をご確認下さい。

より強度の高いパスワードにしてみよう!

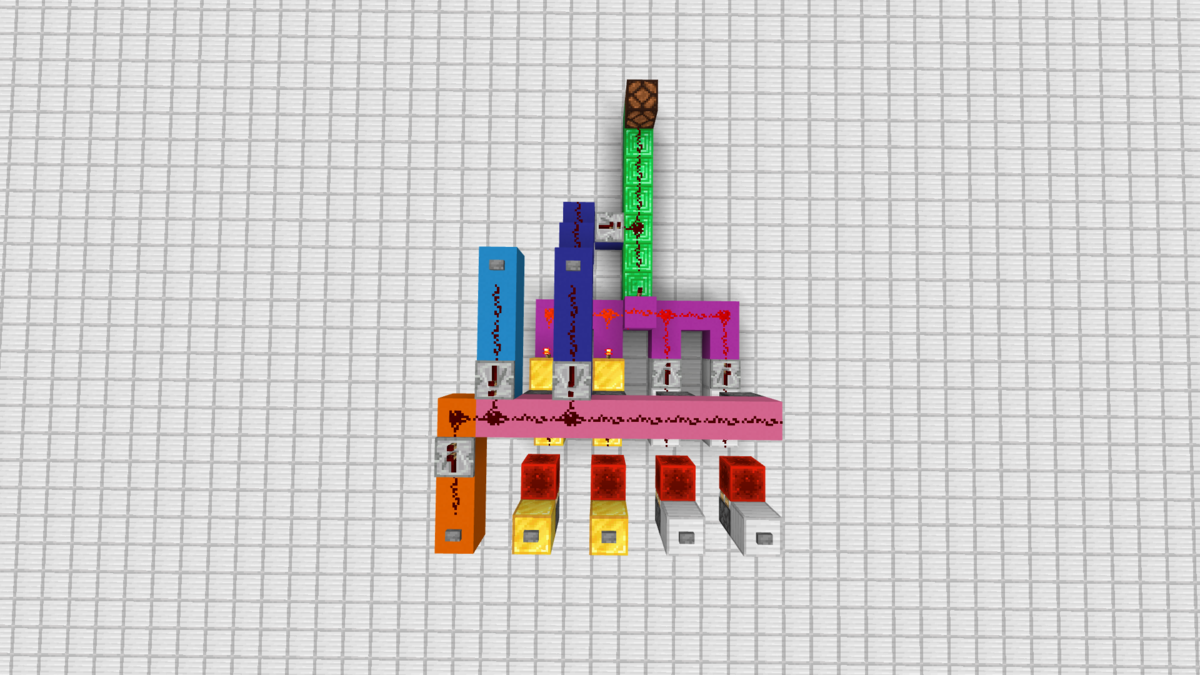

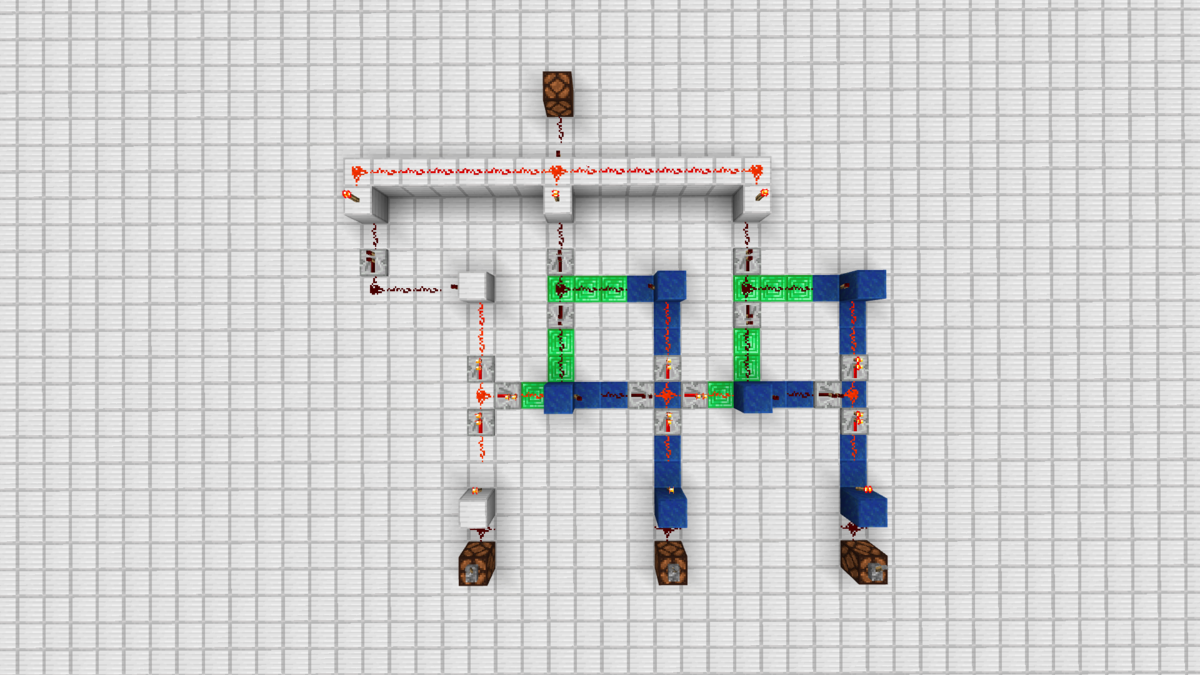

今回は、前回のSR-Latch回路搭載時点でのパスワードドアをベースに進めて行きます。まずはベースとなるパスワードドアをおさらいしましょう。

- 入力:

・金・鉄ブロック :左から入力A, B, C, D、内A, Bが正解

・オレンジコンクリ :外側からのリセット入力R1

・空色コンクリ :内側からのリセット入力R2

・青コンクリ :内側からドアを開ける入力R3

・ピンクコンクリ :Q3をR入力とするSR-Latch回路の入力RA, RB, RC, RD - 出力:

・RSブロック :左からA, B, C, DをそれぞれS入力とするSR-Latch回路の出力QA, QB, QC, QD(の状態)

・金ブロック :QA, QBをそれぞれ入力とするNOT回路の出力QA', QB’

・エメラルドブロック:QA', QB', QC, QDを入力とするNOR回路の出力Q1

・エメラルドブロック:Q1, R3を入力とするOR回路の出力Q2

・ピンクコンクリ :R1, R2, R3を入力とするOR回路の出力Q3 - 論理ゲート:

・赤紫コンクリ :QA', QB', QC, QDを入力とするNOR回路

・エメラルドブロック:Q1, R3を入力とするOR回路

・ピンクコンクリ :R1, R2, R3を入力とするOR回路 - Latch回路:

・RSブロック :A, B, C, DをそれぞれS入力、RA, RB, RC, RDをそれぞれR入力とするSR-Latch回路

動作条件は以下の通りです。

- ドアを開ける条件:

「AとBを入力し、かつCとDを入力しない」または「R3を入力する」 - 鍵をかける(リセットする)条件:

「R1を入力する」または「R2を入力する」または「R3を入力する」

さて、現在のパスワードドア回路でもかなり立派なものですが、もっと複雑なパスワードが設定できるようになったら素敵だと思いませんか?

現在は以下の入力パターンが存在します。

- 1つだけ入力する :4通り

- 2つ入力する :6通り

- 3つ入力する(1つだけ入力しない):4通り

- 全て入力する :1通り

- (合計) :=15通り

しかしながら現在、正解パターンであるAとBのボタン入力については、その順番が関係ありません。もし、ボタン入力の順番も正解のパターンに関係があるようになったら、同じ4ボタンでより多くの入力パターンを作ることができます。

4入力の全てを特定の順番で入力しなければならない時、入力パターンの数は以下の計算式より24通りだと求められます。

4P4 = 4! = 4 * 3 * 2 * 1 = 24

入力パターンが多くなれば、総当たり攻撃(ブルートフォースアタック)に強くなります。より安全なパスワードが設定できるように考えてみましょう!

入力の順番によって出力を変える回路

さてここからは、特定の入力順でのみ1を出力する回路を考えてみます。

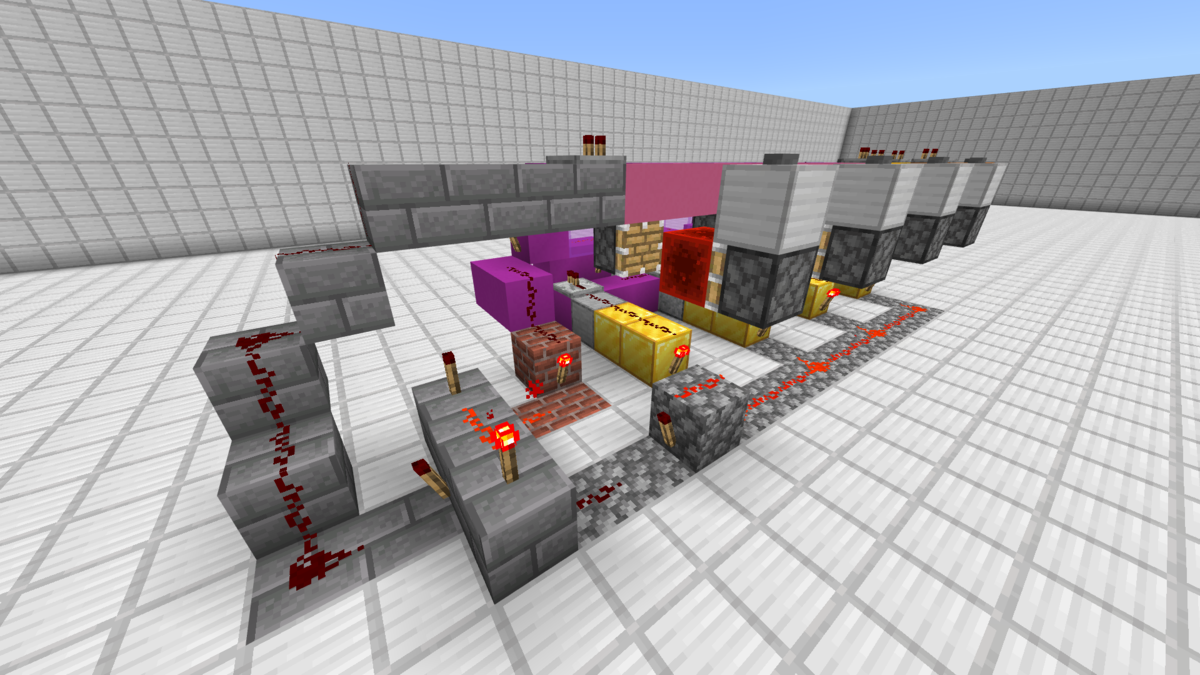

とは言っても結構難しい回路のため、まずは正解を見てそこから「なぜそうなるのか」を解析してみましょう。

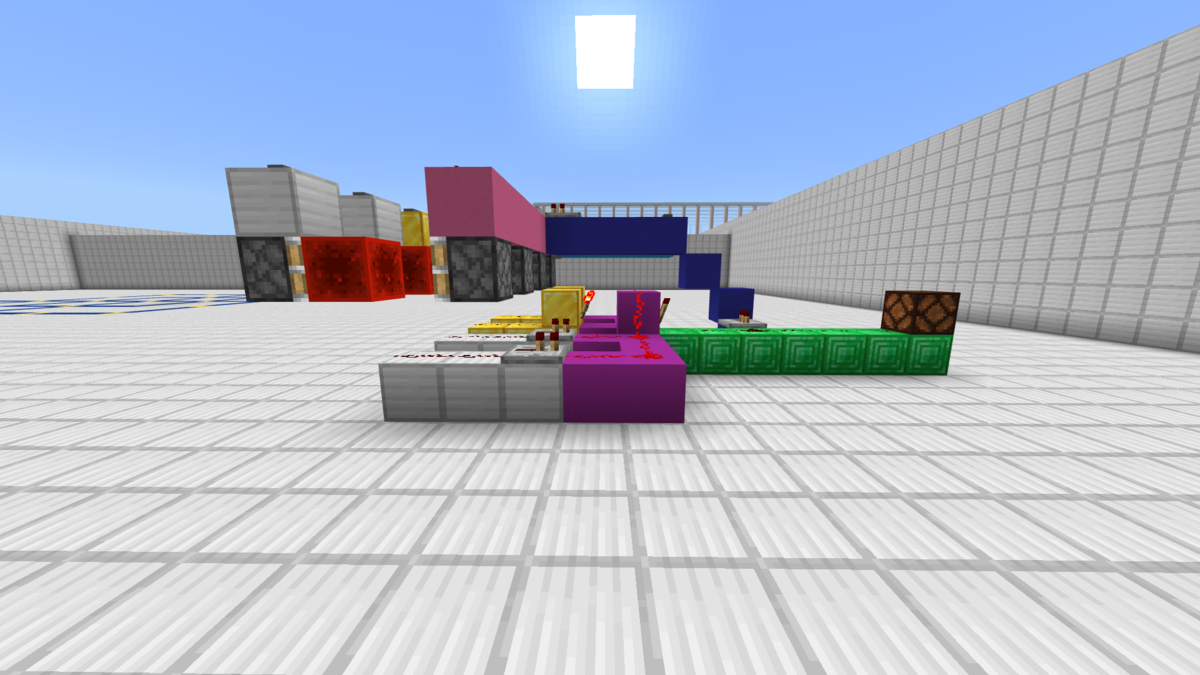

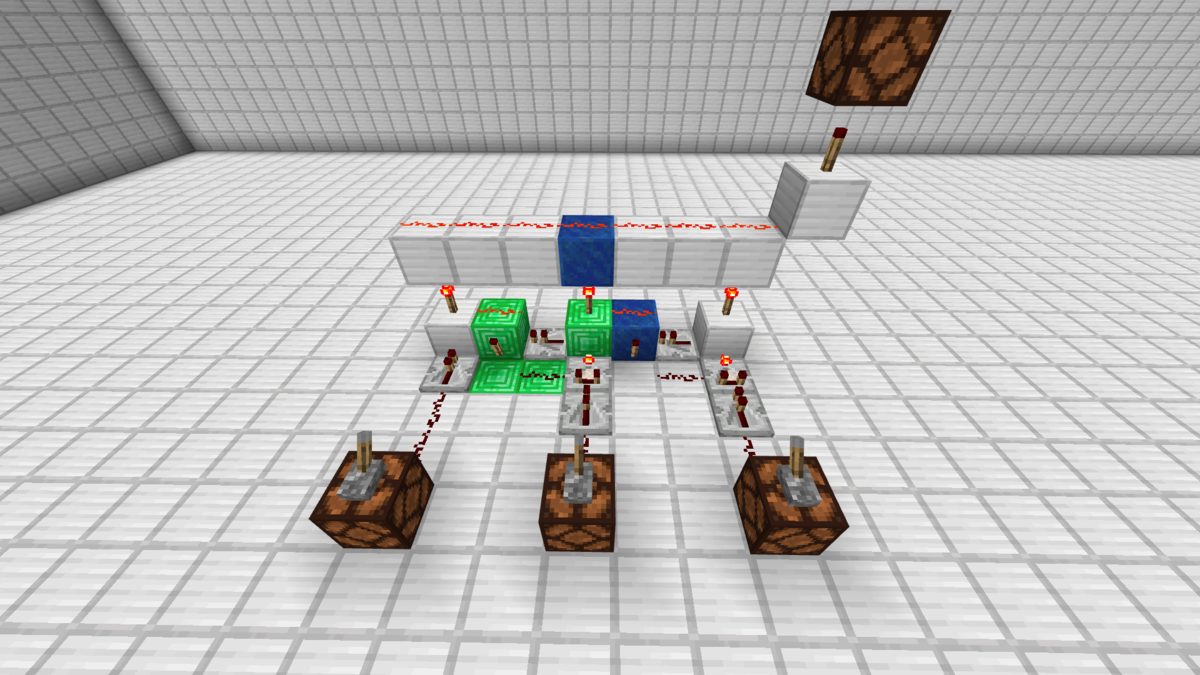

こちらが正解の回路です。青ガラスの部分はガラス等の透過ブロックを、鉄ブロックの部分は不透過ブロックで必ず作って下さい。

…まあ、これではわけわかんないですよね。解説しやすくするために同じ構造の回路をもう少し大きめに、そしてRSワイヤーとRSトーチだけで作ってみます。

RSリピーターも使用されていますが、無くても動作します。このRSリピーターは、RS動力が流れる方向をわかりやすくするために設置しています。

さてこの回路を解析してみますと、SR-Latchに近い構造があることがわかりますね。

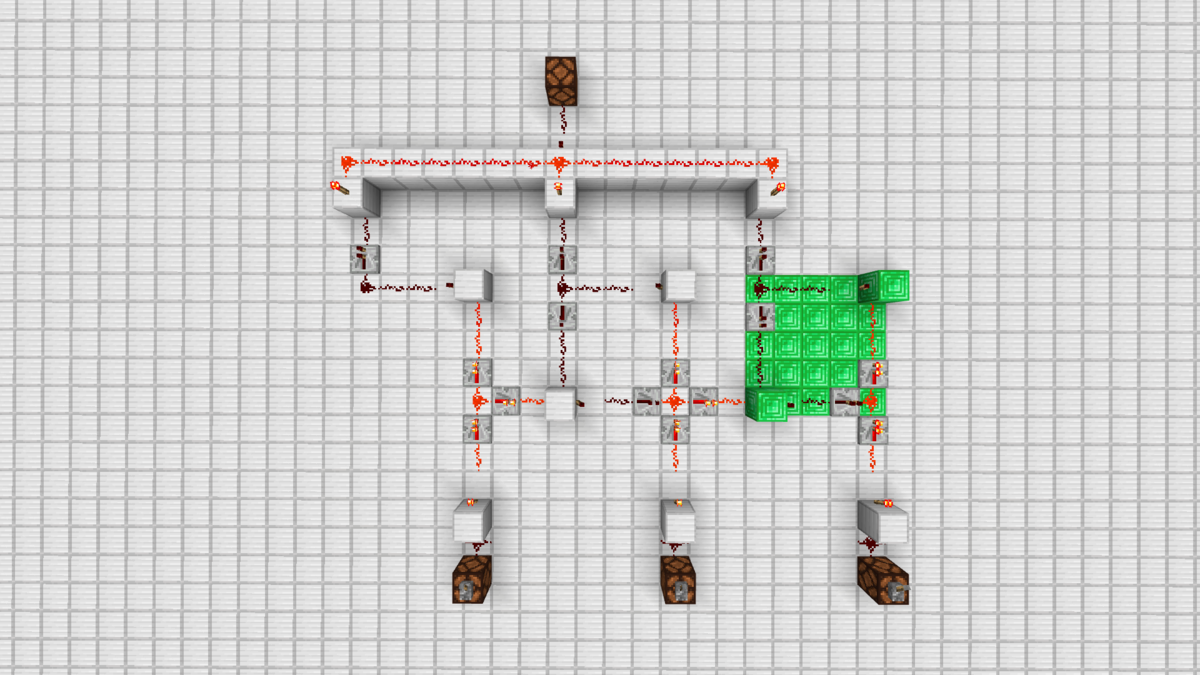

このSR-Latchの周辺をちょっと切り出してみましょう。

少しだけ形が変わっていますが、論理ゲートとLatch回路の構造は同じです。

中央をSR-Latchとすると、この回路は以下の論理ゲート・Latch回路で出来ていることがわかります。

- 入出力:

・右入力=A

・Aを入力とするNOT回路の出力=A'

・左入力=B

・Bを入力とするNOT回路の出力=B'

・SR-Latchの出力=Q

・SR-Latchの逆側出力=notQ

・エメラルドブロック右上=SR-LatchのR入力

・エメラルドブロック左下=SR-LatchのS入力

・notQ, A'を入力とするOR回路の出力=S'

・Q, B'を入力とするOR回路の出力=R' - 論理ゲート:

・Aを入力とするNOT回路

・Bを入力とするNOT回路

・S, A'を入力とするOR回路

・Q, B'を入力とするOR回路 - Latch回路:

・R'をS入力、S'をR入力とするSR-Latch回路

このSR-Latch回路は本来禁止であるS=R=1の状態で静止していますが、この形のSR-Ratch回路はS=R=1の時は必ずQ=0となり、発振が起こらないため回路の動作には問題ありません。

まずはA入力(右のレバー)から考えてみます。

- A入力を1にすると、NOT回路によってA'=0となる

- するとnotQとA'のORが、A'=0, notQ=0によってS'=0となる

- S'=0なのでR入力は0

- 一方左下のQとB'のORはB'=1なのでR'=1となるため、S入力は1

- R入力=0, S入力=1なので、SR-LatchがQ=1となる

- するとQとB'の両方が1になるのでやはりR'=1となり、S入力が1で固定される

このように動作します。続いて、Aを入力したままBを入力して見た時を考えてみます。

- B入力を1にすると、NOT回路によってB'=0となる

- しかしB'=0となってもQ=1のため、R'=1のままでS入力も1のまま

- よってQは変わらず1のまま

このように動作します。ここでAの入力を0に戻してみましょう。

- A入力を0に戻すと、NOT回路によってA'=1となる

- するとnotQとA'のORが、A'=1, notQ=0によってS'=1となる

- そのためS'=1によってR入力が1となり、Q=0になる

- よってQ=0, B'=0のためORを取るとR'=0となり、S入力が0になる

- R入力=1, S入力=0なのでQ=0, notQ=1となる

- するとnotQとA'の両方が1になるのでやはりS'=1となり、R入力が1で固定される

このように動作します。この状態からさらにAの入力を1にしてみましょう。

- A入力を1にすると、NOT回路によってA'=0となる

- しかしA'=0となってもnotQ=1のため、S'=1のままでR入力も1のまま

- よってQは変わらず0のまま

このように動作します。では最後に、この状態からBの入力を0にしてみましょう。

- B入力を0に戻すと、NOT回路によってB'=1となる

- するとQとB'のORが、B'=1, Q=0によってR'=1となる

- そのためR'=1によってS入力が1となり、notQ=0になる

- よってnotQ=0, A'=0のためORを取るとS'=0となり、R入力が0になる

- R入力=0, S入力=1なのでQ=1, notQ=0となる

- するとQとB'の両方が1になるのでやはりR'=1となり、S入力が1で固定される

以上から、以下の真理値表を得られます。なお、AとBは同時に1にはしないものとします(完全に同時タイミングで入力すると発振が起こります)。

- 操作前: A=0, B=0, Q=0 -> A=1, B=0 -> Q=1

- 操作前: A=0, B=0, Q=0 -> A=0, B=1 -> Q=0

- 操作前: A=1, B=0, Q=1 -> A=0, B=0 -> Q=0

- 操作前: A=1, B=0, Q=1 -> A=1, B=1 -> Q=1

- 操作前: A=0, B=1, Q=0 -> A=0, B=0 -> Q=0

- 操作前: A=0, B=1, Q=0 -> A=1, B=1 -> Q=0

- 操作前: A=1, B=1, Q=0 -> A=1, B=0 -> Q=1

- 操作前: A=1, B=1, Q=1 -> A=0, B=1 -> Q=0

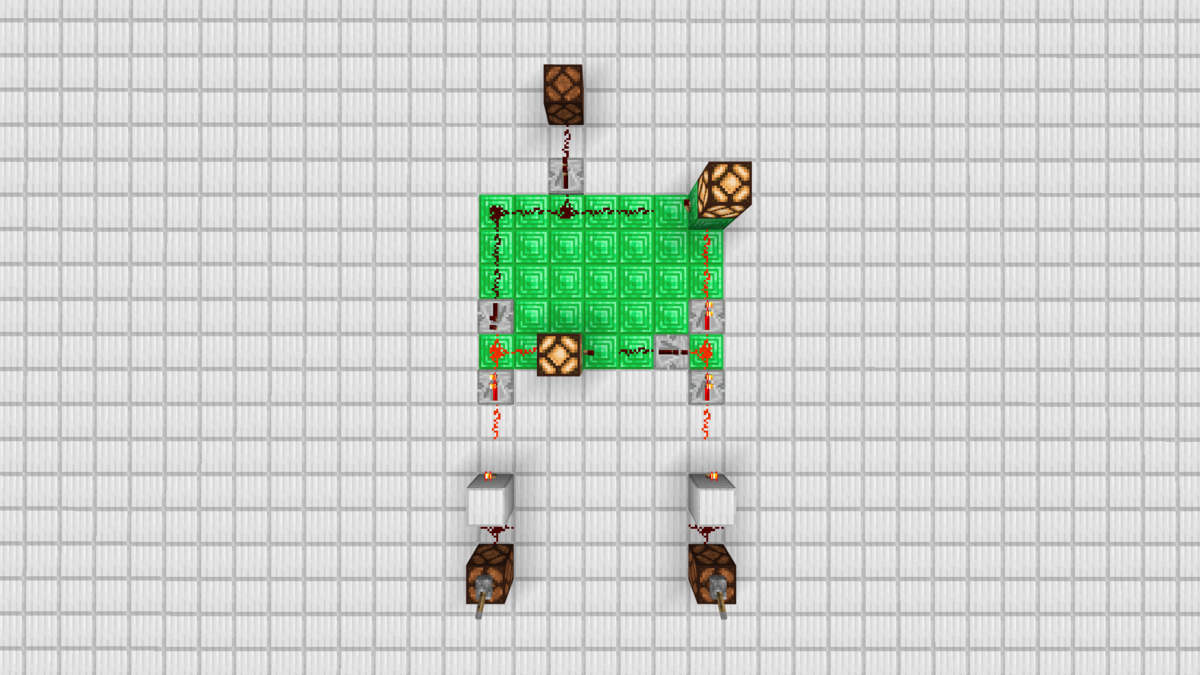

以上より、このエメラルドブロックの部分はSR-Latchとして動きそうなことはわかりましたが、見方を変えると実は3つの論理ゲートで出来ていることがわかります。このように色分けしてみるとわかると思います。

- 入出力:

・右入力=A

・左入力=B

・Bを入力とするNOT回路の出力=B'

・AとQ'を入力とするAND回路の出力=Q

・B'とQを入力とするOR回路の出力=Q' - 論理ゲート:

・金ブロック :Bを入力とするNOT回路

・ラピスブロック :A, Q'を入力とするAND回路

・エメラルドブロック:B', Qを入力とするOR回路

この論理ゲートの組み合わせで動いているとして、もう一度真理値表を書いてみましょう。なお、回路の形そのものは先程までと変わっていないため、AとBを完全に同時に1にするのは禁止です。

- AND回路:

・A=0, Q'=1 -> Q=0

・A=1, Q'=1 -> Q=1

・A=1, Q'=0 -> Q=0

・A=0, Q'=1 -> Q=0 - OR回路:

・Q=0, B'=1-> Q'=1

・Q=1, B'=0 -> Q'=1

・Q=1, B'=0 -> Q'=1

・Q=0, B'=0 -> Q'=0

これらをまとめると真理値表はこのようになります。

- 操作前: A=0, B=0, B'=1, Q=0, Q'=1 -> A=1, B=0, B'=1 -> Q=1, Q'=1

- 操作前: A=0, B=0, B'=1, Q=0, Q'=1 -> A=0, B=1, B'=0 -> Q=0, Q'=0

- 操作前: A=1, B=0, B'=1, Q=1, Q'=1 -> A=0, B=0, B'=1 -> Q=0, Q'=1

- 操作前: A=1, B=0, B'=1, Q=1, Q'=1 -> A=1, B=1, B'=0 -> Q=1, Q'=1

- 操作前: A=0, B=1, B'=0, Q=0, Q'=0 -> A=0, B=0, B'=1 -> Q=0, Q'=1

- 操作前: A=0, B=1, B'=0, Q=0, Q'=0 -> A=1, B=1, B'=0 -> Q=0, Q'=0

- 操作前: A=1, B=1, B'=0, Q=0, Q'=0 -> A=1, B=0, B'=1 -> Q=1, Q'=1

- 操作前: A=1, B=1, B'=0, Q=1, Q'=1 -> A=0, B=1, B'=0 -> Q=0, Q'=0

このように書き出してみると、この形のSR-Latchの動作原理がなんとなく理解できたかと思います。

少し脱線しましたがここで、今回の本題である特定の入力順でのみ出力が1になる回路の制作というところに戻り、この回路を見直してみましょう。

上の真理値表の中で、Q=1となるのは以下の3パターンです。

- 操作前: A=0, B=0, B'=1, Q=0, Q'=1 -> A=1, B=0, B'=1 -> Q=1, Q'=1

- 操作前: A=1, B=0, B'=1, Q=1, Q'=1 -> A=1, B=1, B'=0 -> Q=1, Q'=1

- 操作前: A=1, B=1, B'=0, Q=0, Q'=0 -> A=1, B=0, B'=1 -> Q=1, Q'=1

ここから純粋な入力と出力だけを抽出しつつ、それぞれのパターンはどの順番でAとBの入力をしている想定なのかを見ていきましょう。

- 操作前: A=0, B=0, Q=0 -> A=1, B=0 -> Q=1

・AもBも入力していない状態で、Aをまず入力した - 操作前: A=1, B=0, Q=1 -> A=1, B=1 -> Q=1

・Aを先に入力している状態で、次にBを入力した - 操作前: A=1, B=1, Q=0 -> A=1, B=0 -> Q=1

・Aを入力し、次にBを入力した状態で、Bを0に戻した

さて、今回の本題の想定は「全てのボタン(レバー)を」「特定の順番で」入力するというものでした。そのため、最終的な出力が1になる条件を書き出すと以下の2つになりますね。

- 全ての入力が1になっている

- 特定の順番で入力されている

一見、クリアしているように見えますが、上の出力が1となる3パターンの内、真ん中の入力パターン以外はAしか入力されていないのに出力が1になってしまっています。そのため、真ん中の入力パターンでのみ最終出力が1になるように改造してみましょう。

具体的にどのようにするかというところですが、真ん中の入力パターン以外の2パターンはAしか入力されていないのに出力が1になってしまっているのでしたね。逆を言えば、Bが入力されていないのに出力が1になってしまっていると言えます。

つまり、SR-Latchの出力が1である上でB入力が1である時にのみ最終出力が1になるようにすればいいわけです。

SR-LatchのQ=1かつB=1の時のみ出力=1である回路…もうわかりましたね。QとBを入力とするAND回路を増設してみましょう。

これでついに特定の入力順でのみ出力が1になる回路が完成しました。ここで最初の方のお手本をもう一度振り返ってみましょう。

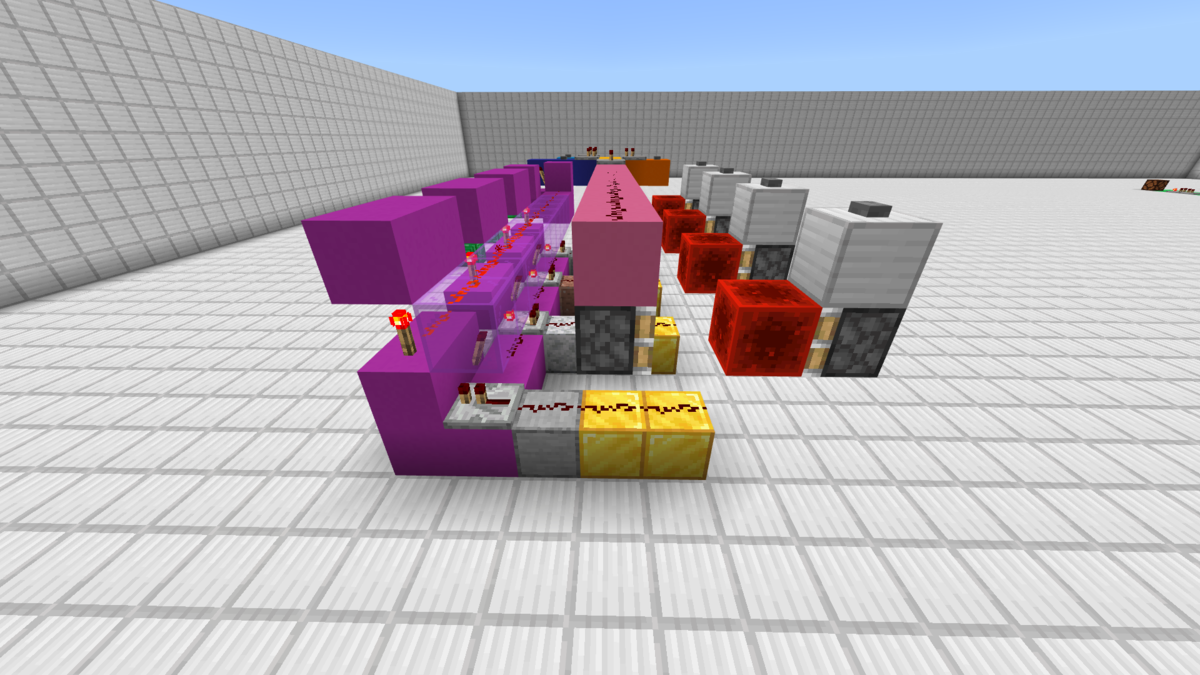

これを見てみると、右側に同じSR-Latchの構造を増設し、同じようにQをAND回路に通している構造なのがわかると思います。ちなみに一番左の構造が微妙に異なりますが、NOT回路で動力を二回反転しているので、入力直結の時と同じ働きをします。

回路を小型化しよう!

さてここからはRS回路の醍醐味(とわたくし個人が勝手に思っている)である回路の小型化をやっていきましょう。

なんで回路の小型化をする必要があるの?という方むけに、回路の小型化のメリットを挙げていきましょう。

- 必要素材が減る

- 必要スペースが減る

- 回路の動作が高速になる

なお、これらのメリットの内「必要スペースの縮小」以外は、小型化によって犠牲になることもありますが、基本的にはこれらの認識で問題ありません。

単純な回路ならこれらのメリットが薄いのですが、今回の様な複雑な回路の場合にはこれらのメリットを多く享受できます。

まあ理由はともかく、RS回路を小型化する具体的な手法を紹介しましょう。

回路の小型化については、大きく分けて以下の2つの手法があるとわたくしは考えています。

- 論理ゲート・Latch回路を別の形にする

- 二重反転とRSワイヤーを減らす

これらの手法を活用し、画像A2-7の回路を画像A2-1の回路に近づけていきましょう。

説明しやすくするため、画像A2-7の回路の入出力と論理ゲートをまとめてみましょう。

- 入出力:

・入力=右からA, B, C

・AとQ1'を入力とするAND回路の出力=Q1

・BQとQ1を入力とするOR回路の出力=Q1'

・BとQ2'を入力とするAND回路の出力=Q2

・BとQ2'を入力とするNAND回路の出力=BQ

・C'とQ2を入力とするOR回路の出力=Q2'

・Cを入力とするNOT回路の出力=C'

・C'を入力とするNOT回路の出力=Q3

・Q1, Q2, Q3を入力とするAND回路の出力=Q - 論理ゲート:

・AとQ1'を入力とするAND回路

・BQとQ1を入力とするOR回路

・BとQ2'を入力とするAND回路

・BとQ2'を入力とするNAND回路

・C'とQ2を入力とするOR回路

・Cを入力とするNOT回路

・C'を入力とするNOT回路

・Q1, Q2, Q3を入力とするAND回路

さて、元の入力を3つにしたことで新たにNAND回路が生まれていますね。しかしこのNAND回路の入力をよく見てみると、同じ入力を使用しているAND回路がありますね。この点を良く覚えておきましょう。

ここで、AND回路の作り方を2種類見ていただきたいと思います。

ラピスブロック部分のAND回路は右のAND回路と全く同じ構造です。今回はラピスブロック部分のAND回路を左のAND回路に置き換えてみましょう。

金ブロックの部分が増えているように見えますが、右側の金ブロックのNOT回路はその左側にあるAND回路の出力を反転しています。つまりこのNOT回路の出力結果はNAND回路のものになるわけです。そのため論理ゲート構造は変わっていません。

左側の金ブロックは二重反転を無くした上で、反転が必要な部分のみを切り出した結果生まれたものです。よって、入出力と論理ゲートが以下の様に整理されました。

- 入出力:

・入力=右からA, B, C

・AとQ1'を入力とするAND回路の出力=Q1

・BQとQ1を入力とするOR回路の出力=Q1'

・BとQ2'を入力とするAND回路の出力=Q2

・BとQ2'を入力とするNAND回路の出力=BQ

・C'とQ2を入力とするOR回路の出力=Q2'

・Cを入力とするNOT回路の出力=C'

・Q1, Q2, Cを入力とするAND回路の出力=Q - 論理ゲート:

・AとQ1'を入力とするAND回路

・BQとQ1を入力とするOR回路

・BとQ2'を入力とするAND回路

・BとQ2'を入力とするNAND回路

・C'とQ2を入力とするOR回路

・Cを入力とするNOT回路

・Q1, Q2, Cを入力とするAND回路

さてこうしてみると、実はNAND回路が2カ所あることにお気づきでしょうか。このように色分けするとわかりやすいと思います。

エメラルドブロックの部分がNAND回路を構成している部分です。そしてラピスブロック部分がそのNAND回路の出力部分です。

同じ入力・出力の論理ゲートが2つあるのは無駄ですよね。これを1つにできると良さそうですね。

さらに、色は付けていませんが左側のC入力についても、上のAND回路をNOR回路とみなせば、C入力を反転しているNOT回路が2つあることに気づいたでしょうか。これもついでに削ってしまいましょう。

RS動力の逆流に気をつけながら整理すると、以下の様になります。

このようになりました。これで画像A2-1の回路と同じ論理ゲート構造の回路になりました。入出力と論理ゲートを確認してみましょう。

- 入出力:

・入力=右からA, B, C

・AとQ1'を入力とするAND回路の出力=Q1

・Q1を入力とするNOT回路の出力=notQ1

・BQとQ1を入力とするOR回路の出力=Q1'

・BとQ2'を入力とするAND回路の出力=Q2

・BとQ2'を入力とするNAND回路の出力=BQ

・C'とQ2を入力とするOR回路の出力=Q2'

・Cを入力とするNOT回路の出力=C'

・notQ1, Q2, C'を入力とするNOR回路の出力=Q - 論理ゲート:

・AとQ1'を入力とするAND回路

・Q1を入力とするNOT回路

・BQとQ1を入力とするOR回路

・BとQ2'を入力とするAND回路

・BとQ2'を入力とするNAND回路

・C'とQ2を入力とするOR回路の出力

・Cを入力とするNOT回路の出力

・notQ1, Q2, C'を入力とするNOR回路

これであとはRSワイヤーを減らすだけで画像A2-1の形になります。ここからは駆け足でやっちゃいましょう。

逆流防止のためにNAND出力やNOT出力にもRSリピーターを設置している

RSトーチもRSリピーターと同様に動力の逆流を防止できるのだ

[画像A2-13] 画像A2-12の状態からQ1'やQ2'を出力するOR回路を縮めた

RSリピーターとRSコンパレーターは側面からRSトーチの入力を

受け付けないのでRS動力は混線しない

RSトーチが上にある不透過ブロックに動力を入力できる性質を利用している

[画像A2-15] 画像A2-14の状態からNOR回路をもっと小型化した

金ブロック部分は混線を避けるため、必ず不透過ブロックを設置

青ガラス部分は下のRSトーチとの混線を避けるため。必ず透過ブロックを設置

通常ガラス部分は何でも良い

[画像A2-15]の状態でようやく[画像A2-1]と全く同じ形の回路になりました。ちなみに途中からRSコンパレーターのメイン入力にRSリピーターが接続されなくなっていますが、これに関しては元々不要でした(動力の流れをわかりやすくするために設置していました)。

順序回路をパスワードドアに搭載する!

今回作成した特定の入力順でのみ出力が1になる回路は、実は順序回路と呼ばれるものでした。前回ご紹介したLatch(FlipFlop)回路も本来、順序回路の種類の一部ですが、当ブログでは今回作った特定の入力順でのみ出力が1になる回路のみを順序回路と呼称することとします。

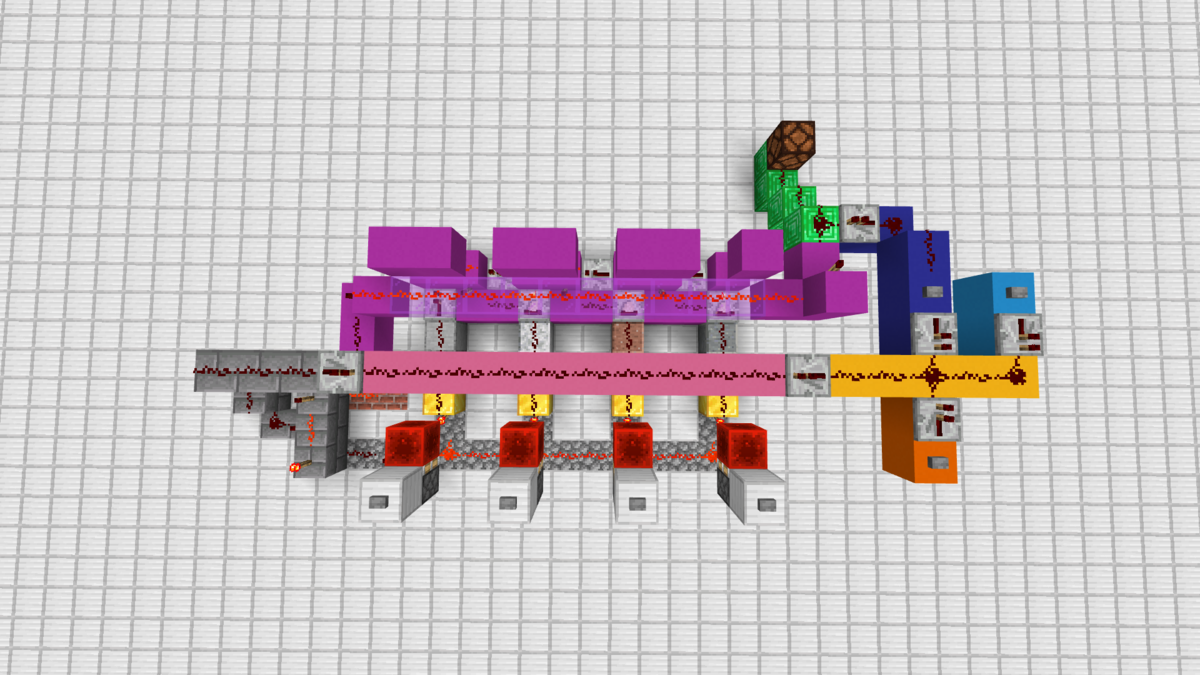

さてこの順序回路の構造ですが、実は最後の入力部分以外は繰り返せる構造になっています。試しに入力を4つに増やしてみましょう。

回路が右に伸びている

回路が右に伸びましたが、同じ作りのものが1セット分増えただけになっています。このように特定の構造を理論上無限に繰り返し繋げることができる回路や論理の構造を繰り返し構造と呼ぶことにします。

この順序回路に限らず、繰り返し構造で作られた回路・論理構造は、それすなわち応用性・拡張性が高いつくりのため、後から改造したり別の何かに利用する際に取れる選択肢が増えます。そのため複雑な回路を設計する時は、なるべく繰り返し構造になるように設計すると、論理ミスを起こしにくくなります。

また話が脱線しましたが、ここでようやく[画像A1-1]のパスワードドアにこの順序回路を搭載してみましょう。

構造としては、[画像A1-1]のパスワードドア回路の4入力のNOR回路を4入力の順列回路に置き換えただけです。

- 入力:

・鉄ブロック :入力=右からA, B, C, D、右から入力するのが正解

・磨かれた安山岩 :順序回路の1番目の入力=N1

・磨かれた花崗岩 :順序回路の2番目の入力=N2

・磨かれた閃緑岩 :順序回路の3番目の入力=N3

・なめらかな石 :順序回路の4番目の入力=N4

・オレンジコンクリ :外側からのリセット入力=R1

・空色コンクリ :内側からのリセット入力=R2

・青コンクリ :内側からドアを開ける入力=R3

・ピンクコンクリ :Q3をR入力とするSR-Latch回路の入力=右からRA, RB, RC, RD - 出力:

・金ブロック :A, B, C, DをそれぞれS入力とするSR-Latch回路の出力=右からQA, QB, QC, QD

・赤紫コンクリ :N1, N2, N3, N4を入力とする順序回路の出力=Q1

・エメラルドブロック:Q1, R3を入力とするOR回路の出力=Q2

・ピンクコンクリ :R1, R2, R3を入力とするOR回路の出力=Q3 - 論理ゲート:

・エメラルドブロック:Q1, R3を入力とするOR回路

・黄コンクリ :R1, R2, R3を入力とするOR回路 - Latch回路:

・RSブロック :A, B, C, DをそれぞれS入力、RA, RB, RC, RDをそれぞれR入力とするSR-Latch回路 - その他:

・赤紫コンクリ :N1, N2, N3, N4を入力とする順序回路

動作条件は以下の様になっています。

- ドアを開ける条件:

「A→B→C→Dの順で入力する」または「R3を入力する」 - 鍵をかける(リセットする)条件:

「R1を入力する」または「R2を入力する」または「R3を入力する」

「ドアを開ける条件」の右側が若干変わりましたが、それ以外は変わりません。入力保持にSR-Latchを使用しているため、鍵をかける(リセットする)条件は変わっていません。

なお、正解パターンの入力順を変えたい時は、SR-Latch出力のQA, QB, QC, QDと順序回路入力のN1, N2, N3, N4の繋ぎ方を変えるだけです。個人で色々試してみて下さい。

順序回路のエラー検知

これで非常に実用的で立派なパスワードドア回路が出来上がりましたが、まだまだ改良できる部分があります。

このパスワードドア回路は特定の順番で4つのボタンを押した時のみ1を出力、つまりドアが開くわけですが、少し見方を変えると4つのボタン全てを押したにもかかわらず1を出力しなかった場合はエラーとみなすこともできます。

プログラムがエラーを検出すると、強制終了等でリセットをかけますよね。このパスワードドア回路にも、入力ボタンを全て押して出力が1にならなかった場合、つまりエラーが発生した場合にそれを検出して入力をリセットする回路を組み込んでみましょう。

さて、エラーの条件を少し書き出してみましょう。

- 4つのボタンが全て入力されている

=> QA=QB=QC=QD=1 - 順序回路の出力が0

=> Q1=0 - 上2つの条件が両方とも満たされている

2つの条件が満たされている必要があるので、「4つのボタンが全て入力されている」の出力と「順序回路の出力が0」の出力をAND回路に入力すれば良さそうですね。

また「4つのボタンが全て入力されている」の検知にもAND回路が使えそうです。よって以下の様に改造してみました。

この回路は以下の回路を追加してできています。

- SR-Latchの出力QA, QB, QC, QDを入力とするAND回路(出力をER1とする)

- 順序回路の出力Q1を反転するNOT回路(出力をER2とする)

- ER1, ER2を入力とするAND回路(出力をR4とする)

- R1, R2, R3, R4を入力とするOR回路(出力は変わらずQ3)

これで一件落着のように見えますが、実はまだ完成しきっていません。

論理上は合っているのですが、実際の回路の処理においてはドアが開くまで若干のラグがあります。そのため、ドアが開いて動力の状態が安定するよりも先に、今追加したエラー検知・リセット回路の方が早く動いてしまいます。

ER1とER2に注目すると、ER2の状態が安定してからこのAND回路が動作すればいいことがなんとなく想像が付きます。そのため、ER1側に遅延をかけてあげましょう。

これで完全に完成です。とても素晴らしいパスワードドア回路になりましたね!

ちなみに、この今追加した部分の回路はもう少し簡略化できます。ここまで熱心にわたくしの解説を見ていただいた方なら「あれ?ここはもっとこうできるよな?」と気づけるかと思います。

気づけなかった方は、もう一度このパスワードドア回路解説の初級・中級・上級(今回)を見返したり、自分で実際に作ってみると気づけるかと思います。皆さん各自で色々研究してみて下さい!

今回はここまでです。前回と比べてさらに難易度が跳ね上がりましたが、この記事を見ながら自分で実際に作ったり考えたりすれば、必ず少しずつ理解を深めていけるはずです。「なんだかよくわからんな?」という方も、まずは見よう見まねで作ってみることをオススメします。見よう見まねでも、実際に体験した方が理解への近道になります。是非ともチャレンジしてみて下さい!

次回はさらにもっともっと超高度な動作をするパスワードドア回路を作っていきます。今回の回路の発展形やダイヤルロック式の鍵等、より高度なロック回路を作ってしまいます。

次回の難易度はいよいよ「超級」に上がりますが、次回の内容までできるようになれば超高度なゲームを作ることができちゃいます。次回もぜひ見て下さい!

次回リンク ↓

(解説ページでき次第、リンク貼ります)

今回のまとめ

- 当ブログでは「特定の入力順でのみ1を出力する回路」を順序回路と呼称します

- 順序回路を使えばより強度の高いパスワードが設定できるようになる!

- 順序回路は実行順序のエラー検出にも応用できる!

- 複雑な実行条件・条件分岐は真理値表を書いて攻略すべし!

関連記事

- コマンド解説-応用編その4:パスワードドアを作ってみよう!超級編-

- コマンド解説-応用編その5:ゲームタイマーを作ってみよう!-

- コマンド解説-応用編その6:ゲーム演出を作ってみよう!初級編-

- コマンド解説-応用編その7:ゲーム演出を作ってみよう!中級編-

- コマンド解説-応用編その8:ゲーム演出を作ってみよう!上級編-

- コマンド解説-応用編その9:謎解きゲームを作ってみよう!初級編-

- コマンド解説-応用編その10:謎解きゲームを作ってみよう!中級編-

- コマンド解説-応用編その11:謎解きゲームを作ってみよう!上級編-

- コマンド解説-応用編その12:スコア稼ぎゲームを作ってみよう!-

- コマンド解説-応用編その13:特殊アイテムを作ってみよう!初級編-

- コマンド解説-応用編その14:特殊アイテムを作ってみよう!中級編-

- コマンド解説-応用編その15:特殊アイテムを作ってみよう!上級編-

※解説ページができ次第リンクさせます

当記事及び当ブログへのご意見・ご質問はいつでも受け付けております。

お気軽にコメント欄までどうぞ!

↓良ければポチッとお願いします。